Silicon wafers are the cornerstone of semiconductor materials. They are first made into silicon rods by pulling single crystals, and then cut and made. Since the number of valence electrons of silicon atoms is 4 and the ordinal number is moderate, silicon has special physical and chemical properties and can be used in chemical, photovoltaic, chip and other fields. Especially in the field of chips, it is the semiconductor properties of silicon that make it the cornerstone of chips. In the field of photovoltaics, it can be used for solar power generation. Moreover, silicon accounts for 25.8% of the earth's crust. It is relatively convenient to mine and has strong recyclability, so the price is low, which further enhances the application range of silicon.

1. Silicon - the cornerstone of chip materials Silicon materials are divided into single crystal silicon and polycrystalline silicon according to the different arrangement of unit cells. The biggest difference between single crystal silicon and polycrystalline silicon is that the unit cell arrangement of single crystal silicon is orderly, while polycrystalline silicon is disordered. In terms of manufacturing methods, polycrystalline silicon is generally made by directly pouring silicon material into a crucible to melt it and then cooling it. Monocrystalline silicon is formed into a crystal rod by pulling a single crystal (the Czochralski method). In terms of physical properties, the characteristics of the two types of silicon are quite different. Monocrystalline silicon has strong electrical conductivity and high photoelectric conversion efficiency. The photoelectric conversion efficiency of monocrystalline silicon is generally around 17% to 25%, while the efficiency of polycrystalline silicon is below 15%.

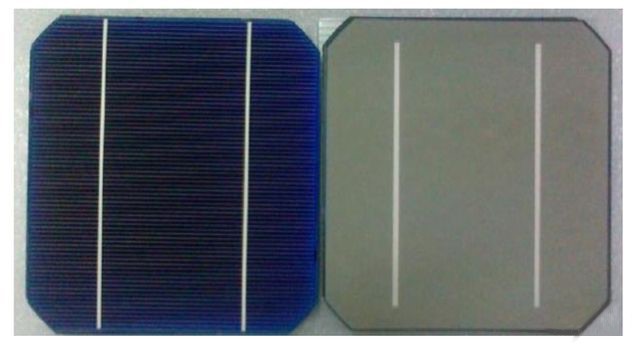

▲Semiconductor silicon wafers and photovoltaic silicon wafers

▲Single crystal silicon unit cell structure

Photovoltaic silicon wafers: Due to the photoelectric effect and the obvious advantages of monocrystalline silicon, people use silicon wafers to complete the conversion of solar energy into electrical energy. In the photovoltaic field, the square monocrystalline silicon cells with rounded corners are generally used. Cheaper polycrystalline silicon wafers are also used, but the conversion efficiency is lower.

▲Front and back of monocrystalline silicon cell

▲Polycrystalline silicon cell front and back

Since photovoltaic silicon wafers have low requirements for parameters such as purity and warpage, the manufacturing process is relatively simple. Taking monocrystalline silicon cells as an example, the first step is to cut and round. First, cut the monocrystalline silicon rod into square rods according to the size requirements, and then round the four corners of the square rods. The second step is pickling, which is mainly to remove surface impurities of the monocrystalline square rods. The third step is slicing. First, paste the cleaned square rods to the work board. Then put the work board on the slicer and cut it according to the set process parameters. Finally, clean the monocrystalline silicon wafers and monitor the surface smoothness, resistivity and other parameters.

Semiconductor silicon wafers: Semiconductor silicon wafers have higher requirements than photovoltaic silicon wafers. First, all silicon wafers used in the semiconductor industry are monocrystalline silicon, in order to ensure the same electrical properties of each position of the silicon wafer. In terms of shape and size, photovoltaic monocrystalline silicon wafers are square, mainly with side lengths of 125mm, 150mm, and 156mm. The monocrystalline silicon wafers used for semiconductors are round, with diameters of 150mm (6-inch wafers), 200mm (8-inch wafers) and 300mm (12-inch wafers). In terms of purity, the purity requirement for monocrystalline silicon wafers used for photovoltaics is between 4N-6N (99.99%-99.9999%), but the purity requirement for monocrystalline silicon wafers used for semiconductors is around 9N (99.9999999%)-11N (99.999999999%), and the minimum purity requirement is 1000 times that of monocrystalline silicon wafers used for photovoltaics. In terms of appearance, the surface flatness, smoothness and cleanliness of silicon wafers used for semiconductors are higher than those of silicon wafers used for photovoltaics. Purity is the biggest difference between monocrystalline silicon wafers used for photovoltaics and monocrystalline silicon wafers used for semiconductors.

▲Semiconductor silicon wafer manufacturing process

The development of Moore's Law is the development of silicon wafers. Since semiconductor silicon wafers are round, semiconductor silicon wafers are also called "silicon wafers" or "wafers". Wafers are the "substrate" for chip manufacturing, and all chips are manufactured on this "substrate". In the development history of semiconductor silicon wafers, there are two main directions: size and structure.

In terms of size, the development path of silicon wafers is getting bigger and bigger: in the early stage of integrated circuit development, 0.75-inch wafers were used. Increasing the wafer area and the number of chips on a single wafer can reduce costs. Around 1965, with the introduction of Moore's Law, both integrated circuit technology and silicon wafers ushered in a period of rapid development. Silicon wafers have gone through 4-inch, 6-inch, 8-inch and 12-inch nodes. Since Intel and IBM jointly developed 12-inch wafer chip manufacturing in 2001, the current mainstream silicon wafer is 12-inch wafers, accounting for about 70%, but 18-inch (450mm) wafers have been put on the agenda.

▲Parameters of different wafer sizes

▲The development of silicon wafer size

In terms of structure, the development direction of silicon wafers is becoming more and more complex: in the early stage of integrated circuit development, there was only one kind of logic chip, but with the increasing number of application scenarios, logic chips, power devices, analog chips, mixed analog and digital chips, flash/DRAM storage chips, radio frequency chips, etc. have appeared one after another, making silicon wafers have different structural forms. Now, there are mainly three types:

PW (Polish Wafer): polished wafer. The silicon wafers directly cut after pulling single crystals are not perfect in smoothness or warping, so they must first be polished. This method is also the most primitive way to process silicon wafers.

AW (Anneal Wafer): Annealed wafer. With the continuous development of process technology and the continuous reduction of transistor feature sizes, the shortcomings of polished wafers are gradually exposed, such as local lattice defects on the surface of silicon wafers and high oxygen content on the surface of silicon wafers. In order to solve these problems, annealing wafer technology has been developed. After polishing, the silicon wafer is placed in a furnace tube filled with inert gas (usually argon) for high-temperature annealing. This can not only repair the lattice defects on the surface of the silicon wafer, but also reduce the surface oxygen content.

EW (Epitaxy Wafer): epitaxial silicon wafer. With the increasing application scenarios of integrated circuits, the standard silicon wafers manufactured by silicon wafer factories can no longer meet the requirements of some products in terms of electrical properties. At the same time, the lattice defects reduced by thermal annealing cannot meet the increasingly smaller line width requirements. This has led to the emergence of epitaxial silicon wafers. The usual epitaxial layer is a silicon thin film. A layer of silicon thin film is grown on the basis of the original silicon wafer using thin film deposition technology. Since the silicon substrate exists as a seed crystal in silicon epitaxy, the growth of the epitaxial layer will replicate the crystal structure of the silicon wafer. Since the substrate silicon wafer is a single crystal, the epitaxial layer is also a single crystal. However, since it is not polished, the lattice defects on the surface of the silicon wafer after growth can be reduced to a very low level.

Epitaxy technical indicators mainly include epitaxial layer thickness and its uniformity, resistivity uniformity, body metal control, particle control, stacking faults, dislocations and other defect control. At this stage, people have achieved high epitaxial silicon wafer quality by optimizing the epitaxy reaction temperature, epitaxy gas flow rate, and center and edge temperature gradients. Due to different products and the need for technological upgrades, the epitaxial process has been continuously optimized to achieve high epitaxial silicon wafer quality.

In addition, current technology can generate epitaxial layers with resistivity doping elements and doping concentrations different from those of the original silicon wafer, which makes it easier to control the electrical properties of the grown silicon wafer. For example, a layer of N-type silicon epitaxial layer can be generated on a P-type silicon wafer, thus forming a low-concentration doped PN junction, which can optimize the breakdown voltage and reduce the latch effect in subsequent chip manufacturing. The thickness of the epitaxial layer generally varies according to the usage scenario. Generally, the thickness of the logic chip is about 0.5 microns to 5 microns, and the thickness of the power device is about 50 microns to 100 microns because it needs to withstand high voltage.

▲Epitaxial silicon wafer growth process

▲Different doping of epitaxial wafers

SW (SOI Wafer): SOI stands for Silicon-On-Insulator. SOI silicon wafers are often used in RF front-end chips because of their advantages such as small parasitic capacitance, small short channel effect, high inheritance density, high speed, low power consumption, and especially low substrate noise.

▲Ordinary silicon MOS structure

▲SOI silicon wafer MOS structure

There are four main methods for manufacturing SOI silicon wafers: SIMOX technology, Bonding technology, Sim-bond technology and Smart-CutTM technology; the principle of SOI silicon wafers is relatively simple, and the core goal is to add an insulating layer (generally mainly silicon dioxide SiO2) in the middle of the substrate.

▲Four technologies for manufacturing SOI wafers

From the perspective of performance parameters, Smart-CutTM technology is the most excellent performance in the current SOI silicon wafer manufacturing technology. The performance of Simbond technology is not much different from that of Smart-Cut technology, but in terms of the thickness of the top silicon, the SOI silicon wafer produced by Smart-Cut technology is thinner, and from the perspective of production cost, Smart-Cut technology can reuse silicon wafers. For future mass production, Smart-Cut technology has more cost advantages, so the industry now generally recognizes Smart-Cut technology as the future development direction of SOI silicon wafers.

▲Performance comparison of different SOI wafer manufacturing technologies

SIMOX technology: SIMOX stands for Separation by Implanted Oxygen. Oxygen atoms are injected into the wafer, and then annealed at high temperature to react with the surrounding silicon atoms to form a layer of silicon dioxide. The difficulty of this technology is to control the depth and thickness of oxygen ion implantation. It has high requirements for ion implantation technology.

Bonding technology: Bonding technology is also called bonding technology. SOI silicon wafers made by bonding are also called Bonded SOI, or BSOI for short. Bonding technology requires two ordinary silicon wafers, one of which is grown with an oxide layer (SiO2), and then bonded with another silicon source. The connection is the oxide layer. Finally, it is ground and polished to the desired depth of the buried layer (SiO2). Since bonding technology is simpler than ion implantation technology, most SOI silicon wafers are currently made using bonding technology.

▲Silicon-on-insulator

▲Wafer bonding method to form silicon on insulator

Sim-bond technology: oxygen injection bonding technology. Sim-bond technology is a combination of SIMOX and bond technology. The advantage is that the thickness of the buried oxide layer can be controlled with high precision. The first step is to inject oxygen ions into a silicon wafer, then anneal at high temperature to form an oxide layer, and then form a SiO2 oxide layer on the surface of the silicon wafer. The second step is to bond the silicon wafer to another wafer. Then anneal at high temperature to form a perfect bonding interface. The third step is the thinning process. Thinning is performed using CMP technology, but unlike bond technology, sim-bond has a self-stop layer, which will automatically stop when grinding to the SiO2 layer. Then the SiO2 layer is removed by etching. The last step is polishing.

Smart-cut technology: smart peeling technology. Smart-cut technology is an extension of bonding technology. The first step is to oxidize a wafer and generate a fixed thickness of SiO2 on the surface of the wafer. The second step is to use ion implantation technology to inject hydrogen ions into a fixed depth of the wafer. The third step is to bond another wafer to the oxidized wafer. The fourth step is to use low-temperature thermal annealing technology to form bubbles with hydrogen ions, which causes a portion of the silicon wafer to peel off. Then high-temperature thermal annealing technology is used to increase the bonding strength. The fifth step is to flatten the silicon surface. This technology is internationally recognized as the development direction of SOI technology. The thickness of the buried oxide layer is completely determined by the depth of hydrogen ion implantation, which is more accurate. Moreover, the peeled wafer can be reused, which greatly reduces the cost.

▲SIM-bond method to form silicon-on-insulator

▲Smart-cut method to form silicon-on-insulator

二. High-barrier manufacturing technology 1. Manufacturing technology

The raw material of silicon wafers is quartz, which is commonly known as sand, which can be mined directly in nature. The wafer manufacturing process can be completed in several steps: mainly deoxidation and purification, refining polysilicon, single crystal silicon ingots (silicon rods), rolling, wafer cutting, wafer polishing, annealing, testing, packaging and other steps.

▲CZ (Czochralski) semiconductor wafer manufacturing process

▲CZ Farad single crystal schematic

Deoxidation and purification: The first step in silicon wafer manufacturing is to deoxidize and purify the quartz ore. The main processes include sorting, magnetic separation, flotation, high-temperature degassing, etc. The main iron and aluminum impurities in the ore are removed.

Refining polysilicon: After obtaining relatively pure SiO2, single crystal silicon is generated through chemical reactions. The main reaction is SiO2+C→Si+CO. After the reaction is completed, CO evaporates directly, so only silicon crystals are left. At this time, the silicon is polycrystalline silicon, and it is crude silicon, containing a lot of impurities. In order to filter out excess impurities, the obtained crude silicon must be pickled. Commonly used acids are hydrochloric acid (HCl), sulfuric acid (H2SO4), etc. The silicon content after soaking in acid is generally above 99.7%. During the pickling process, although iron, aluminum and other elements are also dissolved in the acid and filtered out. However, silicon also reacts with acid to generate SiHCl3 (trichlorosilane) or SiCl4 (silicon tetrachloride). However, both substances are in gaseous state, so after pickling, the original impurities such as iron and aluminum have been dissolved in the acid, but silicon has become gaseous. Finally, the high-purity gaseous SiHCl3 or SiCl4 is reduced with hydrogen to obtain high-purity polycrystalline silicon.

The CZ method produces single crystal silicon: silicon wafers are mainly used in logic and memory chips, with a market share of about 95%; the CZ method originated from Czochralski's drawing of thin filaments from molten metal in 1918, so it is also called the CZ method. This is the mainstream technology for growing single crystal silicon today. The main process is to put polycrystalline silicon in a crucible, heat it to melt it, and then clamp a single crystal silicon seed crystal and suspend it above the crucible. When pulling it vertically, one end is inserted into the melt until it melts, and then it is slowly rotated and pulled upward. In this way, the interface between the liquid and the solid will gradually condense to form a single crystal. Since the whole process can be regarded as a process of replicating the seed crystal, the generated silicon crystal is single crystal silicon. In addition, the doping of the wafer is also carried out in the process of pulling the single crystal, usually in liquid phase doping and gas phase doping. Liquid phase doping refers to the addition of P-type or N-type elements into the crucible. During the process of pulling single crystals, these elements can be directly pulled into the silicon rod.

▲CZ Faraday single crystal method

▲Silicon rod after pulling single crystal

Diameter rolling: Since it is difficult to control the diameter of the single crystal silicon rod during the process of pulling the single crystal, in order to obtain the silicon rod of standard diameter, such as 6 inches, 8 inches, 12 inches, etc. After pulling the single crystal, the diameter of the silicon ingot will be rolled. The surface of the silicon rod after rolling is smooth and the size error is smaller.

Cutting chamfering: After obtaining the silicon ingot, the wafer is cut. The silicon ingot is placed on a fixed cutting machine and cut according to the set cutting program. Since the thickness of the silicon wafer is small, the edge of the cut silicon wafer is very sharp. The purpose of chamfering is to form a smooth edge. The chamfered silicon wafer has a lower center stress, which makes it more solid and not easy to break in the future chip manufacturing.

Polishing: The main purpose of polishing is to make the surface of the wafer smoother, flat and damage-free, and to ensure the thickness consistency of each wafer.

Test packaging: After obtaining the polished silicon wafer, the electrical properties of the silicon wafer need to be tested, such as resistivity and other parameters. Most silicon wafer factories have epitaxial wafer services. If epitaxial wafers are needed, epitaxial wafer growth will be carried out. If the epitaxial wafer is not needed, it will be packaged and shipped to other epitaxial wafer factories or wafer factories.

Zone melting method (FZ): Silicon wafers made by this method are mainly used in some power chips, with a market share of about 4%; silicon wafers made by FZ (zone melting method) are mainly used as power devices. And the size of silicon wafers is mainly 8 inches and 6 inches. Currently, about 15% of silicon wafers are made by zone melting method. Compared with silicon wafers made by CZ method, the biggest feature of FZ method is that it has relatively high resistivity, higher purity, and can withstand high voltage, but it is difficult to make large-size wafers, and the mechanical properties are poor, so it is often used for power device silicon wafers, and is rarely used in integrated circuits.

There are three steps in making single crystal silicon rods by zone melting method:

1. Heat polycrystalline silicon, contact with seed crystal, and rotate downward to pull single crystal. In a furnace chamber under vacuum or inert gas environment, use electric field to heat the polycrystalline silicon rod until the polycrystalline silicon in the heated area melts to form a molten zone.

2. Contact the molten zone with seed crystal and melt it.

3. By moving the electric field heating position, the molten zone on the polysilicon moves upward continuously, while the seed crystal slowly rotates and stretches downward, gradually forming a single crystal silicon rod. Because the zone melting method does not use a crucible, many pollution sources are avoided, and the single crystal pulled by the zone melting method has the characteristics of high purity.

▲FZ Farad single crystal space structure

▲Schematic diagram of FZ single crystal pulling

2. Manufacturing cost

Semiconductor silicon wafers have higher requirements for purity and electrical properties than new energy silicon wafers, so more purification steps and raw material supply are required in the manufacturing process, resulting in a more diverse range of manufacturing raw materials. Therefore, the proportion of silicon material cost is relatively reduced, but the proportion of manufacturing expenses will be relatively increased.

For semiconductor silicon wafers, raw material cost is the main cost, accounting for about 47% of the main business cost. The second is manufacturing expenses, accounting for about 38.6%. Similar to the semiconductor manufacturing industry, the silicon wafer industry is a capital-intensive industry with high demand for fixed asset investment, which will generate high manufacturing expenses due to depreciation of fixed assets such as machinery and equipment. Finally, direct labor costs account for about 14.4%.

Among the raw material costs of silicon wafer manufacturing, polysilicon is the main raw material, accounting for about 30.7%. The second is packaging materials, accounting for about 17.0%. Since semiconductor silicon wafers have high requirements for cleanliness and vacuum, especially for silicon wafers, which are easily oxidized, the requirements for packaging are much higher than those for new energy silicon wafers. Therefore, in the cost structure, packaging materials account for a high proportion. Quartz crucibles account for about 8.7% of the raw material cost. The quartz crucible used in semiconductor silicon wafer manufacturing is also a disposable crucible, but the physical and thermal properties of the crucible are more demanding. Polishing fluid, grinding wheel, and polishing pad account for 13.8% in total and are mainly used in the silicon wafer polishing process.

▲Operating cost structure of silicon industry in 2018

▲Raw material composition of silicon industry in 2018

Water and electricity costs account for about 15% of the manufacturing cost: In the manufacturing cost, the total water and electricity costs account for about 15% of the entire manufacturing cost, of which electricity costs account for about 11.4% and water costs account for about 3.4%. In terms of corresponding amounts, according to the 2018 financial data of the Silicon Industry Group, the total cost of electricity and water costs is equivalent to the cost of packaging materials, accounting for about half of the polysilicon material. The electricity cost is slightly higher than that of quartz crucibles by about 20%.

▲Proportion of silicon industry manufacturing costs in 2018

▲ Partial cost composition of Silicon Industry Group in 2018 (Unit: 10,000 yuan)

3,Four barriers to silicon wafer manufacturing

The barriers to silicon wafers are relatively high, especially for semiconductor silicon wafers. There are four main barriers: technical barriers, certification barriers, equipment barriers, and capital barriers.

▲ The main barriers to the silicon wafer manufacturing industry

Technical barriers: The technical indicators of silicon wafers are relatively large. In addition to the common size, polishing thickness, etc., there are also warpage, resistivity, curvature, etc. of silicon wafers. In terms of mainstream 300mm silicon wafers, due to the high uniformity requirements of advanced processes for silicon wafers, compared with 200mm wafers, parameters such as flatness, warpage, curvature, and surface metal residue are added to monitor the quality requirements of 300mm silicon wafers. In terms of purity, advanced process silicon wafers are required to be around 9N (99.9999999%)-11N (99.999999999%), which is the main technical barrier for silicon wafer suppliers.

Silicon wafers are highly customized products; purity is the most basic parameter of silicon wafers and also the main technical barrier. In addition, silicon wafers are not universal products and cannot be copied. The specifications of large silicon wafers in various wafer foundries are completely different, and the different uses of various terminal products will also lead to completely different requirements for silicon wafers. This requires silicon wafer manufacturers to design and manufacture different silicon wafers according to different end-customer products, which further increases the difficulty of silicon wafer supply.

▲Profit forecast of the company's business segments

Certification barriers: Chip manufacturers have strict requirements on the quality of various raw materials and are very cautious in selecting suppliers. There are high barriers to entering the supplier list of chip manufacturers. Usually, chip manufacturers will require silicon wafer suppliers to provide some silicon wafers for trial production, and most of them are used for test wafers, not wafer mass production wafers. After passing the test wafers, small batches of mass production wafers will be trial-produced. After passing the internal certification, the chip manufacturer will send the products to downstream customers. After obtaining their customer certification, the silicon wafer supplier will be finally certified and the purchase contract will be signed. It takes a long time for the products of semiconductor silicon wafer companies to enter the supply chain of chip manufacturers. The certification cycle for new suppliers takes at least 12-18 months.

In addition, the certification barriers from test wafers to mass production wafers: At present, most of the 12-inch wafers in China remain in the supply of test wafers, but the certification procedures for test wafers are completely different from those for mass production wafers, and the certification standards for mass production silicon wafers are more stringent. Since test silicon wafers do not manufacture chips, they only need to be certified by the wafer foundry itself, and they only need to be certified at the current manufacturing site. However, for mass-produced silicon wafers, they must be certified by terminal fabless customers and monitored at all steps of the entire manufacturing process before they can be supplied in batches. Generally speaking, in order to maintain the stability of silicon wafer supply and chip yield. Once a wafer manufacturer and a silicon wafer supplier establish a supply relationship, they will not easily change suppliers, and both parties will establish a feedback mechanism to meet personalized needs, and the stickiness between silicon wafer suppliers and customers will continue to increase. If a new silicon wafer manufacturer joins the ranks of suppliers, it must provide a closer cooperative relationship and higher silicon wafer quality than the original supplier. Therefore, in the silicon wafer industry, the stickiness between silicon wafer suppliers and wafer manufacturers is relatively large, and it is difficult for new suppliers to break the stickiness.

Equipment barriers: The core equipment for manufacturing silicon wafers is the single crystal furnace, which can be described as the "photolithography machine" in silicon wafers. The single crystal furnaces of international mainstream silicon wafer manufacturers are all manufactured by themselves. For example, the single crystal furnaces of Shin-Etsu and SUMCO are independently designed and manufactured by the company or designed and manufactured through holding subsidiaries, and other silicon wafer manufacturers cannot purchase them. Other major silicon wafer manufacturers have their own independent single crystal furnace suppliers and sign strict confidentiality agreements, which makes it impossible for external silicon wafer manufacturers to purchase, or they can only purchase ordinary single crystal furnaces, but cannot supply high-specification single crystal furnaces. Therefore, equipment barriers are also the reason why domestic manufacturers cannot enter the mainstream suppliers of global silicon wafers.

Capital barriers: The manufacturing process of semiconductor silicon wafers is complex, requiring the purchase of advanced and expensive production equipment, and also requires continuous modification and debugging according to the different needs of customers. Due to the high fixed costs such as equipment depreciation, changes in downstream demand have a greater impact on the capacity utilization of silicon wafer companies, and thus on the profits of silicon wafer manufacturing companies. In particular, companies that have just entered the silicon wafer industry have almost been in a loss-making state before they have reached scale shipments, and have high requirements for capital barriers. In addition, due to the long certification cycle of wafer fabs for silicon wafers, silicon wafer manufacturers need to continue to invest during this period, which also requires a lot of funds.

三. Will still be the king of semiconductor materials At present, the semiconductor wafer market is dominated by silicon materials. Silicon materials account for about 95% of the entire semiconductor market. Other materials are mainly compound semiconductor materials, mainly second-generation semiconductor material GaAs wafers and third-generation semiconductor materials SiC and GaN wafers. Among them, silicon wafers are mainly logic chips, memory chips, etc., and are the most widely used semiconductor wafer materials. GaAs wafers are mainly RF chips, and the main application scenarios are low voltage and high frequency; third-generation semiconductor materials are mainly high-power and high-frequency chips, and the main application scenarios are high frequency and high power.

▲Wafer material ratio

▲Application scope of wafers of different materials

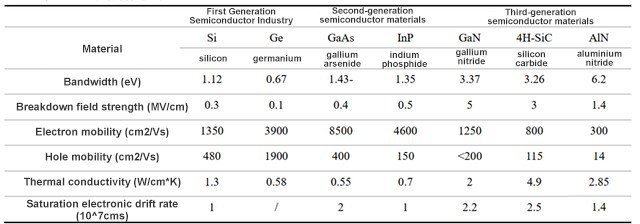

Compound semiconductors and silicon materials are not in a competitive relationship, but a complementary relationship; the development laws of semiconductor materials (especially wafers, substrates and epitaxial wafer materials) include three routes, namely size, speed and power, and the three routes correspond to the first, second and third generation semiconductor materials.

▲Performance comparison of first/second/third generation materials

First-generation semiconductor materials: Large-size route: The first-generation semiconductor materials refer to silicon materials. Silicon materials are the earliest developed wafer materials, and are also the materials with the most mature technology, the lowest cost, and the most complete industrial chain at this stage. At the same time, as the size of silicon wafers increases, the cost of a single chip decreases. The main application areas are logic chips and low-voltage, low-power fields. The size of silicon wafers ranges from 2 inches, 4 inches, 6 inches, 8 inches, to today's mainstream 12-inch wafer technology. Typical silicon wafer companies include Japan's Shin-Etsu Chemical, Sumco, etc. At present, the main international wafer fabs use silicon materials as the main production material.

▲Comparison of different wafer sizes

Second-generation semiconductor materials: high-speed route. Since the chip needs to be able to withstand high-frequency switching in the RF circuit, the second-generation semiconductor wafer was invented. The main application field is RF circuit, and the typical terminal field is the RF chip of mobile terminals such as mobile phones. The second-generation semiconductor is mainly represented by GaAs (gallium arsenide) and InP (indium phosphide), among which GaAs is the commonly used mobile terminal RF chip material today. Typical foundry companies include Taiwan Win Semiconductors, Macronix, Skyworks, Qorvo, etc., which are RF chip IDM companies. The current mainstream is 4-inch and 6-inch wafers.

Third-generation semiconductor materials: high-power route: almost at the same starting point, with the most opportunities. The third route is to increase the power, which will promote its widespread application in the field of high-power circuits. The main materials are SiC and GaN. The main terminals are industrial, automotive and other fields. The power route developed IGBT chips on silicon materials, while SiC (silicon carbide) and GaN (gallium nitride) materials have higher performance than IGBT. At present, SiC wafers are mainly 4-inch and 6-inch, and GaN materials are mainly 6-inch and 8-inch. The world's major foundries include Cree and Wolfspeed in the United States and X-Fab in Germany. However, in this field, the development of international giants is also relatively slow. Domestic companies such as Sanan Optoelectronics, although there is still a certain gap in technology level, are in the initial stage of the entire industry and are most likely to break the foreign monopoly and occupy a place in the international power foundry map.

Compound materials require silicon substrates: Although there are currently a large number of SiC and GaN wafer chips, such as the GaN chargers released by Xiaomi, OPPO, and Realme, and the model3 released by Tesla uses SiC MOSFET instead of IGBT. However, for wafers, most consumer compound semiconductor chips currently use silicon wafers as substrates, and then make compound epitaxial wafers, and then make chips on epitaxial wafers.

The cost of compound semiconductor wafers is relatively high: At present, due to the incompleteness of the compound semiconductor industry chain, the compound semiconductor production capacity is low and the price of compound semiconductor wafers is relatively high. This leads to low end-user acceptance, and the mainstream solution for consumer electronics is still "silicon substrate + compound epitaxial wafer". In the automotive field, silicon-based IGBT is still the mainstream solution. Silicon-based IGBT chips have low costs and a wide range of optional voltages. The price of SiC MOSFET devices is 6 to 10 times that of silicon-based IGBTs. Comparing the performance parameters of SiC-MOSFET and Si-IGBT under Infineon's 650V/20A technical parameters, SiC-MOSFET is still superior to Si-IGBT in terms of performance parameters, but in terms of price, SiC-MOSFET is 7 times that of Si-IGBT. Moreover, as the on-resistance of SiC devices decreases, the price of SiC-MOSFET increases exponentially. For example, when the on-resistance is 45 milliohms, the SiC-MOSFET is only $57.6, when the on-resistance is 11 milliohms, the price is $159.11, and when the on-resistance is equal to 6 milliohms, the price has reached $310.98.

▲Infineon SiC-MOSFET vs. Si-IGBT Comparison

▲Infineon SiC-MOSFET price and on-resistance relationship

四, Domestic efforts have created huge market potential.

1. The silicon wafer market is entering a growth cycle.

The proportion of semiconductor manufacturing materials has increased year by year. Semiconductor materials can be divided into packaging materials and manufacturing materials (including silicon wafers and various chemicals, etc.). In the long run, semiconductor manufacturing materials and packaging materials are in the same trend. However, since 2011, with the continuous development of advanced processes, the consumption of semiconductor manufacturing materials has gradually increased, and the gap between manufacturing materials and packaging materials has gradually increased. In 2018, the sales of manufacturing materials were US$32.2 billion, and the sales of packaging materials were US$19.7 billion, and the manufacturing materials were about 1.6 times that of packaging materials. Among semiconductor materials, manufacturing materials account for about 62% and packaging materials account for 38%.

▲Proportion of semiconductor material consumption in 2018

▲Semiconductor manufacturing material cost ratio

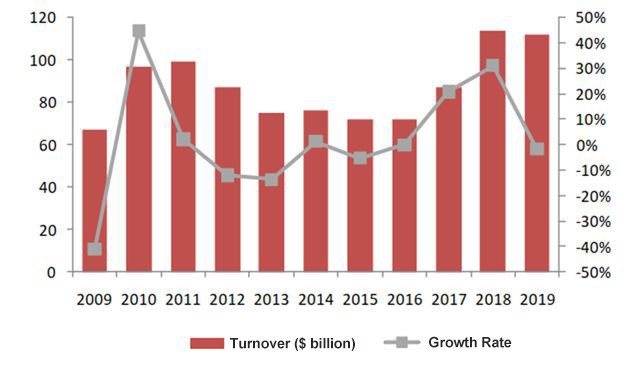

Silicon wafers are the largest consumables in semiconductor manufacturing; among manufacturing materials, silicon wafers, as the raw materials of semiconductors, account for the largest proportion, reaching 37%. Since 2017, with the defeat of Lee Sedol by "AlphaGo", new star technologies led by artificial intelligence have been the main technologies driving the development of global semiconductors. In particular, in 2018, the global demand for memory surged, coupled with the outbreak of blockchain technology, and the demand for silicon wafers hit a record high. The increase in global semiconductor shipments has also driven the rapid increase in silicon wafer shipments. In terms of shipments, in 2018, the global silicon wafer shipment area exceeded 10 billion square inches for the first time, reaching 12.7 billion square inches. In 2019, due to trade frictions in the first half of the year, the shipment area decreased to 11.8 billion square inches. In terms of market turnover, the global market sales in 2018 were US$11.4 billion, and in 2019 it reached US$11.2 billion.

▲2009-2019 Global Silicon Wafer Shipment Area

▲2009-2019 Global Silicon Wafer Sales

From the perspective of wafer segmentation, due to the high cost of second-generation and third-generation semiconductor materials, and the fact that most compound semiconductors are based on silicon wafers, silicon wafers account for 95% of global wafer substrates. From the perspective of specific wafer sizes, 12-inch wafers are the main type of global silicon wafers. In 2018, 12-inch wafers accounted for 64% of global silicon wafer shipments, and 8-inch wafers accounted for 26%.

▲Silicon wafer shipment ratio by size

From the perspective of terminal applications, the global consumption of 12-inch wafers is mainly memory chips, with Nand Flash and DRAM memory accounting for about 75% in total, of which Nand Flash consumes about 33% of wafers, and Nand flash has 35% of the downstream market in the smartphone market. It can be seen that the increase in smartphone shipments and capacity is the main factor driving the shipment of 12-inch wafers. Among 12-inch wafers, logic chips account for about 25%, DRAM accounts for about 22.2%, and other chips such as CIS account for about 20%.

2. China's semiconductor silicon wafer market has huge space

China's semiconductor material market has grown steadily. In 2018, global semiconductor material sales reached US$51.94 billion, a year-on-year increase of 10.7%. Among them, China's sales were US$8.44 billion. Unlike the global market, China's semiconductor material sales have been growing since 2010, and have grown at a rate of more than 10% for three consecutive years from 2016 to 2018. The global semiconductor material market is greatly affected by cyclical factors, especially in Taiwan, China and South Korea, where the fluctuations are large. The North American and European markets are almost in a state of zero growth. Japan's semiconductor materials have been in a state of negative growth for a long time. Globally, only the semiconductor material market in mainland China is in a long-term growth window. The Chinese semiconductor material market is in sharp contrast with the global market.

▲Global semiconductor material sales and growth rate (in billion US dollars)

▲Annual sales of semiconductor materials by country and region (Unit: billion U.S. dollars)

Global semiconductor materials are gradually shifting to the Chinese mainland market. From the sales share of various countries and regions, the top three countries or regions accounted for 55% in 2018, and the regional concentration effect is evident. Among them, Taiwan, China accounts for about 23% of the global wafer production capacity, making it the region with the largest production capacity in the world. Its semiconductor material sales are US$11.4 billion, accounting for 22% of the world, ranking first, and it has been the world's largest semiconductor material consumption region for nine consecutive years. South Korea accounts for about 20% of the global wafer production capacity, with semiconductor material sales of US$8.72 billion, accounting for 17%, ranking second. Mainland China accounts for about 13% of the global production capacity, with semiconductor material sales of US$8.44 billion, accounting for about 16% of the world, ranking third. However, in the long run, the market share of semiconductor materials in mainland China has increased year by year, from 7.5% in 2007 to 16.2% in 2018. Global semiconductor materials are gradually shifting to the Chinese mainland market.

▲ Sales share by country and region in 2018

▲ Semiconductor material sales and share in mainland China (in billion U.S. dollars)

Global wafer production capacity will usher in explosive growth. The 12-inch wafer fab, which represents the most advanced technology in today's wafer fabs, was at its peak in construction from 2017 to 2019, with an average of 8 12-inch wafer fabs added each year worldwide. It is estimated that by 2023, there will be 138 12-inch wafer fabs in the world. According to IC Insight statistics, due to the uncertainty of the Sino-US trade war in the first half of 2019, major wafer fabs around the world postponed their capacity increase plans, but did not cancel them. With the recovery of Sino-US trade in the second half of 2019 and the outbreak of the 5G market, the global wafer production capacity in 2019 still maintained an increase of 7.2 million pieces. However, with the arrival of the 5G market replacement wave, global wafer production capacity will usher in a peak period of increase from 2020 to 2022, with the three-year increase of 17.9 million pieces, 20.8 million pieces and 14.4 million pieces respectively, and will set a record high in 2021. These wafer capacities will be in South Korea (Samsung, Hynix), Taiwan (TSMC) and mainland China (Yangtze River Storage, Changxin Storage, SMIC, Huahong Semiconductor, etc.). Mainland China will account for 50% of the capacity increase.

▲Number of 12-inch wafer fabs worldwide, 2002-2023

▲ Global production capacity increase (unit: million pieces/year, 8-inch equivalent wafer)

The construction of wafer fabs in mainland China will usher in a period of rapid growth. Since 2016, mainland China has begun to actively invest in the construction of wafer fabs, and a wave of factory construction has been set off. According to SEMI's forecast, 62 wafer fabs will be built and put into production in the world from 2017 to 2020, of which 26 will be in China, accounting for 42% of the total. The number of construction in 2018 was 13, accounting for 50% of the expansion. The result of expansion is bound to lead to an increase in capital expenditure and equipment expenditure for wafer fabs. According to SEMI, by 2020, the installed capacity of wafer fabs in mainland China will reach 4 million 8-inch equivalent wafers per month, compared with 2.3 million in 2015, with an annual compound growth rate of 12%, which is much higher than other regions. At the same time, the National Big Fund has also invested heavily in the semiconductor manufacturing industry. In the first phase of the Big Fund's investment, the manufacturing industry accounted for as much as 67%, far higher than the design industry and the packaging and testing industry.

▲2010-2020 China's semiconductor wafer fab investment (Unit: US$ 100 million)

▲Investment ratio of the first phase of the National Big Fund

As of the end of 2019, there are still 9 8-inch wafer fabs and 10 12-inch wafer fabs under construction or planning in China. In addition, since most of China's 12-inch wafer fabs are currently in trial production or small-batch production, they are at the bottom of production capacity. After obtaining product verification from customers and market verification, the production capacity will enter a ramp-up phase, and there will be a huge demand for upstream raw materials.

▲New wafer fabs in China

The popularity of 5G has led to an increase in the silicon content of terminals: from the era of smartphones starting with the iPhone 3, to the 4G mobile phones represented by the iPhone 5, and finally to the current era of 5G mobile phones. The silicon content of mobile phones continues to increase. According to the material cost analysis of mobile phones by dismantling organizations such as tech insights and iFixit, the unit value of the main chips of mobile phones, such as mobile phone processors (AP), baseband processing chips (BP), memory (Nand flash, DRAM), camera modules (CIS), radio frequency chips (RF), power management chips (PMIC), Bluetooth/wifi chips, etc., has shown a gradual increase, and the proportion of the total value of the unit has increased year by year. Although in the iPhone X stage, the proportion of chips decreased due to changes in the screen, with subsequent continuous optimization, the proportion of chip costs has also increased year by year. By the iPhone 11 pro max era, the peak of 4G mobile phones, the proportion of main chips has reached 55%, and the value of a single unit is about US$272. In the evolution from iPhone 3 to iPhone 11 Pro Max, the mobile phone camera has changed from single shot to 3 shots, the body memory has increased from 8GB to 512GB, the proportion of silicon content per unit has increased from 37% to 55%, and the value per unit has increased from US$68 to US$272.

2020 is the first year of mass production of 5G mobile phones. According to the disassembly analysis of the Samsung S20 and Xiaomi 10 mobile phones that have been released, the value and proportion of the main chips per unit have further increased compared with 4G mobile phones. For Samsung, the main chips account for 63.4% of the total material cost, and the value per unit has reached US$335, which is 23% higher than iPhone 11 Pro Max. For Xiaomi, the proportion of main chips is even higher, reaching 68.3%, and the value per unit of main chips has also reached US$300. According to the disassembly of Samsung S20 and Xiaomi 10, it is estimated that the main chips in the initial 5G mobile phones will account for about 65%~70%, and the value of a single machine will be around US$300-330.

▲BOM cost breakdown of mainstream smartphones

▲ Cost ratio of main chips in different mobile phones

The construction of wafer fabs increases the demand for silicon wafers: the expansion of wafer fab capacity will inevitably lead to an increase in the demand for silicon wafers. At present, China has invested heavily in wafer fabs, forming a memory industry dominated by Yangtze Memory Technologies and Hefei Changxin, a logic chip industry dominated by SMIC, a specialty process production line dominated by Huahong Semiconductor and Jetta Semiconductor, and a power device foundry dominated by China Resources Microelectronics and Silan Microelectronics. At present, the growth rate of silicon wafer sales in mainland China in 2017/2018 is higher than 40%. And benefiting from the trend of large fund investment and domestic substitution, downstream wafer fabs have fully expanded their production capacity, driving an increase in demand for upstream silicon wafers. According to SUMCO's forecast, in 2020, the demand for 8-inch silicon wafers in mainland China will be about 970,000 pieces, and 12-inch wafers will reach 1.05 million pieces.

▲China mainland silicon wafer sales and growth rate (Unit: US$ billion)

▲Changes in silicon wafer demand in mainland China (unit: 10,000 pieces/month)

Price increase cycle + advanced process promotes "price" increase: According to the historical silicon wafer price calculation, it is currently at the beginning of a new round of price increase cycle. From 2009 to 2011, smartphones quickly became popular, the silicon content of mobile phones increased, and the price of silicon per unit area continued to rise, reaching $1.09/square inch in 2011. Later, with the increase in silicon wafer inventory and the decline in smartphone sales, the price of silicon wafers per unit area continued to fall, and reached its lowest point in 2016, at $0.67/square inch. In 2016, Google's "AlphaGo" defeated Lee Sedol, allowing artificial intelligence to enter the stage of history. The global demand for silicon wafers increased, entering a new round of price increase cycle. With the release of 5G mobile phones in 2019, the price of silicon wafers per unit area reached $0.94. With the large-scale release of 5G mobile phones in 2020, driving global demand for silicon wafers, it is expected that there will be 2-3 years of price increase space in the future.

Advanced processes drive up prices; semiconductor silicon wafers are the base material for chip manufacturing, and any fluctuations in quality will have a serious impact on the chips. With the continuous development of advanced processes, the impurity requirements for semiconductor silicon wafers are getting higher and higher. Higher requirements make the manufacturing process of silicon wafers more and more difficult, so the price is getting higher and higher. For example, for the same 12-inch silicon wafer, the price of 7nm process silicon wafers is 4.5 times the price of 90nm silicon wafers. At present, the wafer fabs in mainland China are mainly built with 12-inch wafers, and the price of silicon wafers is much higher than that of 8-inch wafers. At the same time, logic chip foundries represented by SMIC and Huahong Semiconductor have gradually transferred the process from 28nm to 16/14nm process, which has increased the overall price of silicon wafers.

Since the 12-inch manufacturing line was first opened in the world in 2000, the market demand has increased significantly. In 2008, the shipment volume exceeded 8-inch silicon wafers for the first time, and in 2009 it exceeded the sum of the shipment area of other sizes of silicon wafers. From 2016 to 2018, due to the booming development of emerging markets such as AI, cloud computing, and blockchain, the compound annual growth rate of 12-inch silicon wafers was 8%. In the future, the market share of 12-inch silicon wafers will continue to increase. According to SUMCO data, there will still be a gap in the global supply and demand of 12-inch silicon wafers in the next 3-5 years, and the gap will become larger and larger as the prosperity of the semiconductor cycle increases. By 2022, there will be a gap of 1000K/month. As an emerging semiconductor manufacturing base in the world, China's huge silicon wafer gap will promote the speed of silicon wafer localization.

According to SUMCO statistics, the sales amount of silicon wafers in mainland China in 2018 was approximately US$930 million, a year-on-year increase of 45%, making it the fastest growing silicon wafer market in the world. Benefiting from the expansion plans of large wafer fabs such as Yangtze Memory, SMIC, and Changxin Storage in 2020-2022. It is estimated that by the end of 2022, the demand for equivalent 12-inch silicon wafers in mainland China will reach 2.01 million per month, with a market space of 20 billion yuan.

Sibranch believes that as the recipient of the third transfer of the semiconductor industry, my country's semiconductor sales share in the global market continues to rise. In addition, my country is the world's largest producer, exporter and consumer of consumer electronics products, and has a large demand for semiconductor products. Therefore, the level of localization will have a great impact on industrial security. As the largest and most basic variety in the wafer manufacturing material market, my country has shortcomings in the field of silicon wafers, and this is more prominent in large silicon wafers. However, with the support of national policies and funds, many Chinese companies have planned production lines and laid out large semiconductor silicon wafers.